Originally Posted by

Ioannis

Very convenient indeed!

Ioannis

Yup, now confirmed. It's faster to use aliases than Richard's module strcpy.

Shared TX pgm:

- loads array with 80 characters (DEC 43 to DEC 122),

- Hserout 80 bytes

Code:

#CONFIG

__config _CONFIG1, _FEXTOSC_OFF & _RSTOSC_HFINT32 & _CLKOUTEN_OFF & _CSWEN_OFF & _FCMEN_ON

__config _CONFIG2, _MCLRE_ON & _PWRTE_OFF & _LPBOREN_OFF & _BOREN_ON & _BORV_LO & _ZCD_OFF & _PPS1WAY_OFF & _STVREN_ON & _DEBUG_OFF

__config _CONFIG3, _WDTCPS_WDTCPS_11 & _WDTE_OFF & _WDTCWS_WDTCWS_7 & _WDTCCS_LFINTOSC

__config _CONFIG4, _WRT_OFF & _SCANE_available & _LVP_OFF

__config _CONFIG5, _CP_OFF & _CPD_OFF

#ENDCONFIG

DEFINE OSC 32

DEFINE HSER_RXREG PORTC

DEFINE HSER_RXBIT 7

DEFINE HSER_TXREG PORTC

DEFINE HSER_TXBIT 6

DEFINE HSER_RCSTA 90h ' Enable serial port & continuous receive

DEFINE HSER_TXSTA 24h ' Enable transmit, BRGH = 1

Define HSER_BAUD 115200

DEFINE HSER_CLROERR 1 ' Clear overflow automatically

DEFINE HSER_SPBRGH 0

DEFINE HSER_SPBRG 68

define CCP1_REG 0 ' Must clear unused CCP pins or else unpredictable results

DEFINE CCP1_BIT 0

define CCP2_REG 0

DEFINE CCP2_BIT 0

define CCP3_REG 0

DEFINE CCP3_BIT 0

define CCP4_REG 0

DEFINE CCP4_BIT 0

define CCP5_REG 0

DEFINE CCP5_BIT 0

;--- Setup registers -----------------------------------------------------------

BAUDCON.3 = 1 ' Enable 16 bit baudrate generator

WPUA = %00100000 ' Pin A7 = Error code 2

' Pin A6 = Error code 1

' Pin A4 = ADC-A4 (B10K)

' Pin A3 = SW external pull-down

' Pin A2 = Vref-

' Pin A1 = ADC-A1 (B5K w/SW)

' Pin A0 = ADC-A0 (B5K)

WPUB = %00111111 ' Pin B7 = ...not available, ICSPDAT

' Pin B6 = ...not available, ICSPCLK

WPUC = %00100111 ' Pin C7 = RX

' Pin C6 = TX

' Pin C4 = ADC-C4 (B10K)

' Pin C3 = ADC-C3 (B10K)

ANSELA = %00000000 ' Pin A7 = Error code 2

' Pin A6 = Error code 1

' Pin A4 = ADC-A4 (B10K)

' Pin A1 = ADC-A1 (B5K w/SW)

' Pin A0 = ADC-A0 (B5K)

ANSELB = %00000000

ANSELC = %00000000 ' Pin C7 = RX

' Pin C6 = TX

' Pin C4 = ADC-C4 (B10K)

' Pin C3 = ADC-C3 (B10K)

TRISA = %00011011 ' Pin A7 = Error code 2

' Pin A6 = Error code 1

' Pin A4 = ADC-A4 (B10K)

' Pin A3 = SW

' Pin A1 = ADC-A1 (B5K w/SW)

' Pin A0 = ADC-A0 (B5K)

TRISB = %00000000 ' Pin B7 = ...not available, ICSPDAT

' Pin B6 = ...not available, ICSPCLK

TRISC = %11011000 ' Pin C7 = RX *** Datasheet requirement, INPUT ***

' Pin C6 = TX *** Datasheet requirement, INPUT ***

' Pin C4 = ADC-C4 (B10K)

' Pin C3 = ADC-C3 (B10K)

Marker1 var LatA.6 ' Pin A7 = Marker 1

Marker2 var LatA.7 ' Pin A6 = Marker 2

MsgData var byte[80]

MsgLoop var byte

MsgLength var byte

Marker1 = 0

Marker2 = 0

MsgLength = 80

Pause 500 ' Let PIC and LCD stabilize

Marker1 = 1

for MsgLoop = 0 to MsgLength - 1

MsgData [MsgLoop] = MsgLoop + 43

next MsgLoop

LatA = %10000000

hserout [ str MsgData\MsgLength ] ' Transmit data

while TX1STA.1 = 0 ' Check TRMT bit

wend

LatA = %00000000

EndlessLoop:

goto EndlessLoop

end

RX pgm using aliases:

- Hserin 80 bytes

- displays array on LCD

Code:

#CONFIG

__config _CONFIG1, _FEXTOSC_OFF & _RSTOSC_HFINT32 & _CLKOUTEN_OFF & _CSWEN_OFF & _FCMEN_ON

__config _CONFIG2, _MCLRE_ON & _PWRTE_OFF & _LPBOREN_OFF & _BOREN_ON & _BORV_LO & _ZCD_OFF & _PPS1WAY_OFF & _STVREN_ON & _DEBUG_OFF

__config _CONFIG3, _WDTCPS_WDTCPS_11 & _WDTE_OFF & _WDTCWS_WDTCWS_7 & _WDTCCS_LFINTOSC

__config _CONFIG4, _WRT_OFF & _SCANE_available & _LVP_OFF

__config _CONFIG5, _CP_OFF & _CPD_OFF

#ENDCONFIG

;--- Interrupts ----------------------------------------------------------------

include "I:\Project_v2\PBP\PBP_Includes\DT_INTS-14_16F1885x-7x.bas"

include "I:\Project_v2\PBP\PBP_Includes\ReEnterPBP.bas"

ASM

INT_LIST macro ; IntSource, Label, Type, ResetFlag?

INT_Handler RX_INT, _RXinterrupt, PBP, no

endm

INT_CREATE ; Creates the interrupt processor

ENDASM

DEFINE OSC 32

DEFINE LCD_DREG PORTB ' Set LCD data port

DEFINE LCD_DBIT 0 ' Set starting data bit

DEFINE LCD_RSREG PORTC ' Set LCD register select port

DEFINE LCD_RSBIT 4 ' Set LCD register select bit

DEFINE LCD_EREG PORTC ' Set LCD enable port

DEFINE LCD_EBIT 5 ' Set LCD enable bit

DEFINE LCD_BITS 4 ' Set LCD bus size

DEFINE LCD_LINES 4 ' Set number of lines on LCD

DEFINE LCD_COMMANDUS 1000 ' Set command delay time in microseconds

DEFINE LCD_DATAUS 50 ' Set data delay time in microseconds

define CCP1_REG 0 ' Must clear unused CCP pins or else unpredictable results

DEFINE CCP1_BIT 0

define CCP2_REG 0

DEFINE CCP2_BIT 0

define CCP3_REG PORTB ' PWM Pulse out to LCD backlight

DEFINE CCP3_BIT 5

define CCP4_REG 0 ' Must clear unused CCP pins or else unpredictable results

DEFINE CCP4_BIT 0

define CCP5_REG PORTA ' PWM Pulse out to LED strips

DEFINE CCP5_BIT 4

DEFINE HSER_RXREG PORTC

DEFINE HSER_RXBIT 7

DEFINE HSER_TXREG PORTC

DEFINE HSER_TXBIT 6

DEFINE HSER_RCSTA 90h ' Enable serial port & continuous receive

DEFINE HSER_TXSTA 24h ' Enable transmit, BRGH = 1

Define HSER_BAUD 115200

DEFINE HSER_CLROERR 1 ' Clear overflow automatically

DEFINE HSER_SPBRGH 0

DEFINE HSER_SPBRG 68

;--- Setup registers -----------------------------------------------------------

BAUDCON.3 = 1 ' Enable 16 bit baudrate generator

INTCON = %11000000 ' INTERRUPT CONTROL REGISTER

' bit 7 GIE: Global Interrupt Enable bit

' 1 = Enables all active interrupts

' 0 = Disables all interrupts

' bit 6 PEIE: Peripheral Interrupt Enable bit

' 1 = Enables all active peripheral interrupts

' 0 = Disables all peripheral interrupts

PIE3 = %00100000 ' PERIPHERAL INTERRUPT ENABLE REGISTER 3

' bit 5 RCIE: USART Receive Interrupt Enable bit

' 1 = Enables the USART receive interrupt

' 0 = Enables the USART receive interrupt

CCP3CON = %10001111 ' CCP3 CONTROL REGISTER

' bit 7 EN: CCPx Module Enable bit

' 1 = CCPx is enabled

' bit 4 FMT: CCPW (Pulse Width) Alignment bit

' MODE = PWM mode

' 0 = Right-aligned format

' bit 3-0 MODE<3:0>: CCPx Mode Select bits(1)

' 1111 = PWM mode

CCP5CON = %10001111 ' CCP5 CONTROL REGISTER

' bit 7 EN: CCPx Module Enable bit

' 1 = CCPx is enabled

' bit 4 FMT: CCPW (Pulse Width) Alignment bit

' MODE = PWM mode

' 0 = Right-aligned format

' bit 3-0 MODE<3:0>: CCPx Mode Select bits(1)

' 1111 = PWM mode

ADCON0 = %00000000 ' Value CONTROL REGISTER 0

WPUA = %00001111 ' Pin A7 = LCDout 2

' Pin A6 = LCDout 1

' Pin A5 = RX Int

' Pin A4 = PWM to LED strips

WPUB = %11011111 ' Pin B7 = ...not available, ICSPDAT

' Pin B6 = ...not available, ICSPCLK

' Pin B5 = PWM to LCD backlight

WPUC = %00111111 ' Pin C7 = RX *** Datasheet requirement, INPUT ***

' Pin C6 = TX *** Datasheet requirement, INPUT ***

ANSELA = %00000000 ' Pin A6 = LCDout 1

' Pin A5 = RX Int

' Pin A4 = PWM to LED strips

ANSELB = %00000000 ' Pin B7 = ...not available, ICSPDAT

' Pin B6 = ...not available, ICSPCLK

' Pin B5 = PWM to LCD backlight

ANSELC = %00000000 ' Pin C7 = RX *** Datasheet requirement, INPUT ***

' Pin C6 = TX *** Datasheet requirement, INPUT ***

TRISA = %00000000 ' Pin A7 = LCDout 2

' Pin A6 = LCDout 1

' Pin A5 = RX Int

' Pin A4 = PWM to LED strips

TRISB = %00000000 ' Pin B7 = ...not available, ICSPDAT

' Pin B6 = ...not available, ICSPCLK

' Pin B5 = PWM to LCD backlight

TRISC = %11000000 ' Pin C7 = RX *** Datasheet requirement, INPUT ***

' Pin C6 = TX *** Datasheet requirement, INPUT ***

Marker2 var LATA.7

Marker1 var LATA.5

MsgData var byte[80]

Value0 VAR MsgData[0] ' LCD row 1

Value1 VAR MsgData[1]

Value2 VAR MsgData[2]

Value3 VAR MsgData[3]

Value4 VAR MsgData[4]

Value5 VAR MsgData[5]

Value6 VAR MsgData[6]

Value7 VAR MsgData[7]

Value8 VAR MsgData[8]

Value9 VAR MsgData[9]

Value10 VAR MsgData[10]

Value11 VAR MsgData[11]

Value12 VAR MsgData[12]

Value13 VAR MsgData[13]

Value14 VAR MsgData[14]

Value15 VAR MsgData[15]

Value16 VAR MsgData[16]

Value17 VAR MsgData[17]

Value18 VAR MsgData[18]

Value19 VAR MsgData[19]

Value20 VAR MsgData[20] ' LCD row 2

Value21 VAR MsgData[21]

Value22 VAR MsgData[22]

Value23 VAR MsgData[23]

Value24 VAR MsgData[24]

Value25 VAR MsgData[25]

Value26 VAR MsgData[26]

Value27 VAR MsgData[27]

Value28 VAR MsgData[28]

Value29 VAR MsgData[29]

Value30 VAR MsgData[30]

Value31 VAR MsgData[31]

Value32 VAR MsgData[32]

Value33 VAR MsgData[33]

Value34 VAR MsgData[34]

Value35 VAR MsgData[35]

Value36 VAR MsgData[36]

Value37 VAR MsgData[37]

Value38 VAR MsgData[38]

Value39 VAR MsgData[39]

Value40 VAR MsgData[40] ' LCD row 3

Value41 VAR MsgData[41]

Value42 VAR MsgData[42]

Value43 VAR MsgData[43]

Value44 VAR MsgData[44]

Value45 VAR MsgData[45]

Value46 VAR MsgData[46]

Value47 VAR MsgData[47]

Value48 VAR MsgData[48]

Value49 VAR MsgData[49]

Value50 VAR MsgData[50]

Value51 VAR MsgData[51]

Value52 VAR MsgData[52]

Value53 VAR MsgData[53]

Value54 VAR MsgData[54]

Value55 VAR MsgData[55]

Value56 VAR MsgData[56]

Value57 VAR MsgData[57]

Value58 VAR MsgData[58]

Value59 VAR MsgData[59]

Value60 VAR MsgData[60] ' LCD row 4

Value61 VAR MsgData[61]

Value62 VAR MsgData[62]

Value63 VAR MsgData[63]

Value64 VAR MsgData[64]

Value65 VAR MsgData[65]

Value66 VAR MsgData[66]

Value67 VAR MsgData[67]

Value68 VAR MsgData[68]

Value69 VAR MsgData[69]

Value70 VAR MsgData[70]

Value71 VAR MsgData[71]

Value72 VAR MsgData[72]

Value73 VAR MsgData[73]

Value74 VAR MsgData[74]

Value75 VAR MsgData[75]

Value76 VAR MsgData[76]

Value77 VAR MsgData[77]

Value78 VAR MsgData[78]

Value79 VAR MsgData[79]

MsgLength var byte

HPWMlcdBL var BYTE

HPWMledstrip var BYTE

RXoccurred var BYTE

MsgLength = 80

Marker1 = 0

Marker2 = 1

HPWMlcdBL = 150 ' low intensity

HPWMledstrip = 15 ' low intensity

HPWM 3, HPWMlcdBL, 1953

HPWM 5, HPWMledstrip, 1953

Marker2 = 0

RXoccurred = 0 ' Clear RX flag

Pause 500 ' Let PIC and LCD stabilize

goto Start ' Jump over sub-routines

;--- Interrupts ----------------------------------------------------------------

RXinterrupt:

Marker1 = 1

hserin [ STR MsgData\MsgLength]

while BAUDCON1.6 = 0 ' Check RCIDL bit

wend

RXoccurred = 1 ' Set flag

Marker1 = 0

@ INT_RETURN

;--- Subroutines ---------------------------------------------------------------

Start:

@ INT_ENABLE RX_INT ; Enable USART Receive interrupts

while RXoccurred = 0 ' Wait for message

wend

Marker2 = 1

LCDOUT $FE, 1

LCDOUT $FE, $80, Value0, Value1, Value2, Value3, Value4, _

Value5, Value6, Value7, Value8, Value9, _

Value10, Value11, Value12, Value13, Value14, _

Value15, Value16, Value17, Value18, Value19

LCDOUT $FE, $C0, Value20, Value21, Value22, Value23, Value24, _

Value25, Value26, Value27, Value28, Value29, _

Value30, Value31, Value32, Value33, Value34, _

Value35, Value36, Value37, Value38, Value39

LCDOUT $FE, $94, Value40, Value41, Value42, Value43, Value44, _

Value45, Value46, Value47, Value48, Value49, _

Value50, Value51, Value52, Value53, Value54, _

Value55, Value56, Value57, Value58, Value59

LCDOUT $FE, $D4, Value60, Value61, Value62, Value63, Value64, _

Value65, Value66, Value67, Value68, Value69, _

Value70, Value71, Value72, Value73, Value74, _

Value75, Value76, Value77, Value78, Value79

Marker2 = 0

EndlessLoop:

goto EndlessLoop

end

RX pgm using strcpy:

- Hserin 80 bytes

- strcpy array

- displays array on LCD

Code:

#CONFIG

__config _CONFIG1, _FEXTOSC_OFF & _RSTOSC_HFINT32 & _CLKOUTEN_OFF & _CSWEN_OFF & _FCMEN_ON

__config _CONFIG2, _MCLRE_ON & _PWRTE_OFF & _LPBOREN_OFF & _BOREN_ON & _BORV_LO & _ZCD_OFF & _PPS1WAY_OFF & _STVREN_ON & _DEBUG_OFF

__config _CONFIG3, _WDTCPS_WDTCPS_11 & _WDTE_OFF & _WDTCWS_WDTCWS_7 & _WDTCCS_LFINTOSC

__config _CONFIG4, _WRT_OFF & _SCANE_available & _LVP_OFF

__config _CONFIG5, _CP_OFF & _CPD_OFF

#ENDCONFIG

include "I:\Project_v2\PBP\PBP_Includes\USARTarray.bas"

;--- Interrupts ----------------------------------------------------------------

include "I:\Project_v2\PBP\PBP_Includes\DT_INTS-14_16F1885x-7x.bas"

include "I:\Project_v2\PBP\PBP_Includes\ReEnterPBP.bas"

ASM

INT_LIST macro ; IntSource, Label, Type, ResetFlag?

INT_Handler RX_INT, _RXinterrupt, PBP, no

endm

INT_CREATE ; Creates the interrupt processor

ENDASM

DEFINE OSC 32

DEFINE LCD_DREG PORTB ' Set LCD data port

DEFINE LCD_DBIT 0 ' Set starting data bit

DEFINE LCD_RSREG PORTC ' Set LCD register select port

DEFINE LCD_RSBIT 4 ' Set LCD register select bit

DEFINE LCD_EREG PORTC ' Set LCD enable port

DEFINE LCD_EBIT 5 ' Set LCD enable bit

DEFINE LCD_BITS 4 ' Set LCD bus size

DEFINE LCD_LINES 4 ' Set number of lines on LCD

DEFINE LCD_COMMANDUS 1000 ' Set command delay time in microseconds

DEFINE LCD_DATAUS 50 ' Set data delay time in microseconds

define CCP1_REG 0 ' Must clear unused CCP pins or else unpredictable results

DEFINE CCP1_BIT 0

define CCP2_REG 0

DEFINE CCP2_BIT 0

define CCP3_REG PORTB ' PWM Pulse out to LCD backlight

DEFINE CCP3_BIT 5

define CCP4_REG 0 ' Must clear unused CCP pins or else unpredictable results

DEFINE CCP4_BIT 0

define CCP5_REG PORTA ' PWM Pulse out to LED strips

DEFINE CCP5_BIT 4

DEFINE HSER_RXREG PORTC

DEFINE HSER_RXBIT 7

DEFINE HSER_TXREG PORTC

DEFINE HSER_TXBIT 6

DEFINE HSER_RCSTA 90h ' Enable serial port & continuous receive

DEFINE HSER_TXSTA 24h ' Enable transmit, BRGH = 1

Define HSER_BAUD 115200

DEFINE HSER_CLROERR 1 ' Clear overflow automatically

DEFINE HSER_SPBRGH 0

DEFINE HSER_SPBRG 68

;--- Setup registers -----------------------------------------------------------

BAUDCON.3 = 1 ' Enable 16 bit baudrate generator

INTCON = %11000000 ' INTERRUPT CONTROL REGISTER

' bit 7 GIE: Global Interrupt Enable bit

' 1 = Enables all active interrupts

' 0 = Disables all interrupts

' bit 6 PEIE: Peripheral Interrupt Enable bit

' 1 = Enables all active peripheral interrupts

' 0 = Disables all peripheral interrupts

PIE3 = %00100000 ' PERIPHERAL INTERRUPT ENABLE REGISTER 3

' bit 5 RCIE: USART Receive Interrupt Enable bit

' 1 = Enables the USART receive interrupt

' 0 = Enables the USART receive interrupt

CCP3CON = %10001111 ' CCP3 CONTROL REGISTER

' bit 7 EN: CCPx Module Enable bit

' 1 = CCPx is enabled

' bit 4 FMT: CCPW (Pulse Width) Alignment bit

' MODE = PWM mode

' 0 = Right-aligned format

' bit 3-0 MODE<3:0>: CCPx Mode Select bits(1)

' 1111 = PWM mode

CCP5CON = %10001111 ' CCP5 CONTROL REGISTER

' bit 7 EN: CCPx Module Enable bit

' 1 = CCPx is enabled

' bit 4 FMT: CCPW (Pulse Width) Alignment bit

' MODE = PWM mode

' 0 = Right-aligned format

' bit 3-0 MODE<3:0>: CCPx Mode Select bits(1)

' 1111 = PWM mode

ADCON0 = %00000000 ' Value CONTROL REGISTER 0

WPUA = %00001111 ' Pin A7 = LCDout 2

' Pin A6 = LCDout 1

' Pin A5 = RX Int

' Pin A4 = PWM to LED strips

WPUB = %11011111 ' Pin B7 = ...not available, ICSPDAT

' Pin B6 = ...not available, ICSPCLK

' Pin B5 = PWM to LCD backlight

WPUC = %00111111 ' Pin C7 = RX *** Datasheet requirement, INPUT ***

' Pin C6 = TX *** Datasheet requirement, INPUT ***

ANSELA = %00000000 ' Pin A6 = LCDout 1

' Pin A5 = RX Int

' Pin A4 = PWM to LED strips

ANSELB = %00000000 ' Pin B7 = ...not available, ICSPDAT

' Pin B6 = ...not available, ICSPCLK

' Pin B5 = PWM to LCD backlight

ANSELC = %00000000 ' Pin C7 = RX *** Datasheet requirement, INPUT ***

' Pin C6 = TX *** Datasheet requirement, INPUT ***

TRISA = %00000000 ' Pin A7 = LCDout 2

' Pin A6 = LCDout 1

' Pin A5 = RX Int

' Pin A4 = PWM to LED strips

TRISB = %00000000 ' Pin B7 = ...not available, ICSPDAT

' Pin B6 = ...not available, ICSPCLK

' Pin B5 = PWM to LCD backlight

TRISC = %11000000 ' Pin C7 = RX *** Datasheet requirement, INPUT ***

' Pin C6 = TX *** Datasheet requirement, INPUT ***

Marker2 var LATA.7

Marker1 var LATA.5

asm

Value0 = _MsgData

Value1 = _MsgData + 1

Value2 = _MsgData + 2

Value3 = _MsgData + 3

Value4 = _MsgData + 4

Value5 = _MsgData + 5

Value6 = _MsgData + 6

Value7 = _MsgData + 7

Value8 = _MsgData + 8

Value9 = _MsgData + 9

Value10 = _MsgData + 10

Value11 = _MsgData + 11

Value12 = _MsgData + 12

Value13 = _MsgData + 13

Value14 = _MsgData + 14

Value15 = _MsgData + 15

Value16 = _MsgData + 16

Value17 = _MsgData + 17

Value18 = _MsgData + 18

Value19 = _MsgData + 19

Value20 = _MsgData + 20

Value21 = _MsgData + 21

Value22 = _MsgData + 22

Value23 = _MsgData + 23

Value24 = _MsgData + 24

Value25 = _MsgData + 25

Value26 = _MsgData + 26

Value27 = _MsgData + 27

Value28 = _MsgData + 28

Value29 = _MsgData + 29

Value30 = _MsgData + 30

Value31 = _MsgData + 31

Value32 = _MsgData + 32

Value33 = _MsgData + 33

Value34 = _MsgData + 34

Value35 = _MsgData + 35

Value36 = _MsgData + 36

Value37 = _MsgData + 37

Value38 = _MsgData + 38

Value39 = _MsgData + 39

Value40 = _MsgData + 40

Value41 = _MsgData + 41

Value42 = _MsgData + 42

Value43 = _MsgData + 43

Value44 = _MsgData + 44

Value45 = _MsgData + 45

Value46 = _MsgData + 46

Value47 = _MsgData + 47

Value48 = _MsgData + 48

Value49 = _MsgData + 49

Value50 = _MsgData + 50

Value51 = _MsgData + 51

Value52 = _MsgData + 52

Value53 = _MsgData + 53

Value54 = _MsgData + 54

Value55 = _MsgData + 55

Value56 = _MsgData + 56

Value57 = _MsgData + 57

Value58 = _MsgData + 58

Value59 = _MsgData + 59

Value60 = _MsgData + 60

Value61 = _MsgData + 61

Value62 = _MsgData + 62

Value63 = _MsgData + 63

Value64 = _MsgData + 64

Value65 = _MsgData + 65

Value66 = _MsgData + 66

Value67 = _MsgData + 67

Value68 = _MsgData + 68

Value69 = _MsgData + 69

Value70 = _MsgData + 70

Value71 = _MsgData + 71

Value72 = _MsgData + 72

Value73 = _MsgData + 73

Value74 = _MsgData + 74

Value75 = _MsgData + 75

Value76 = _MsgData + 76

Value77 = _MsgData + 77

Value78 = _MsgData + 78

Value79 = _MsgData + 79

endasm

Value0 VAR BYTE ext ' LCD row 1

Value1 VAR BYTE ext

Value2 VAR BYTE ext

Value3 VAR BYTE ext

Value4 VAR BYTE ext

Value5 VAR BYTE ext

Value6 VAR BYTE ext

Value7 VAR BYTE ext

Value8 VAR BYTE ext

Value9 VAR BYTE ext

Value10 VAR BYTE ext

Value11 VAR BYTE ext

Value12 VAR BYTE ext

Value13 VAR BYTE ext

Value14 VAR BYTE ext

Value15 VAR BYTE ext

Value16 VAR BYTE ext

Value17 VAR BYTE ext

Value18 VAR BYTE ext

Value19 VAR BYTE ext

Value20 VAR BYTE ext ' LCD row 2

Value21 VAR BYTE ext

Value22 VAR BYTE ext

Value23 VAR BYTE ext

Value24 VAR BYTE ext

Value25 VAR BYTE ext

Value26 VAR BYTE ext

Value27 VAR BYTE ext

Value28 VAR BYTE ext

Value29 VAR BYTE ext

Value30 VAR BYTE ext

Value31 VAR BYTE ext

Value32 VAR BYTE ext

Value33 VAR BYTE ext

Value34 VAR BYTE ext

Value35 VAR BYTE ext

Value36 VAR BYTE ext

Value37 VAR BYTE ext

Value38 VAR BYTE ext

Value39 VAR BYTE ext

Value40 VAR BYTE ext ' LCD row 3

Value41 VAR BYTE ext

Value42 VAR BYTE ext

Value43 VAR BYTE ext

Value44 VAR BYTE ext

Value45 VAR BYTE ext

Value46 VAR BYTE ext

Value47 VAR BYTE ext

Value48 VAR BYTE ext

Value49 VAR BYTE ext

Value50 VAR BYTE ext

Value51 VAR BYTE ext

Value52 VAR BYTE ext

Value53 VAR BYTE ext

Value54 VAR BYTE ext

Value55 VAR BYTE ext

Value56 VAR BYTE ext

Value57 VAR BYTE ext

Value58 VAR BYTE ext

Value59 VAR BYTE ext

Value60 VAR BYTE ext ' LCD row 4

Value61 VAR BYTE ext

Value62 VAR BYTE ext

Value63 VAR BYTE ext

Value64 VAR BYTE ext

Value65 VAR BYTE ext

Value66 VAR BYTE ext

Value67 VAR BYTE ext

Value68 VAR BYTE ext

Value69 VAR BYTE ext

Value70 VAR BYTE ext

Value71 VAR BYTE ext

Value72 VAR BYTE ext

Value73 VAR BYTE ext

Value74 VAR BYTE ext

Value75 VAR BYTE ext

Value76 VAR BYTE ext

Value77 VAR BYTE ext

Value78 VAR BYTE ext

Value79 VAR BYTE ext

Incoming var byte[80]

MsgData var byte[80]

MsgLength var byte

HPWMlcdBL var BYTE

HPWMledstrip var BYTE

RXoccurred var BYTE

MsgLength = 80

Marker1 = 0

Marker2 = 1

HPWMlcdBL = 150 ' low intensity

HPWMledstrip = 15 ' low intensity

HPWM 3, HPWMlcdBL, 1953

HPWM 5, HPWMledstrip, 1953

Marker2 = 0

RXoccurred = 0 ' Clear RX flag

Pause 500 ' Let PIC and LCD stabilize

goto Start ' Jump over sub-routines

;--- Interrupts ----------------------------------------------------------------

RXinterrupt:

Marker1 = 1

hserin [ STR Incoming\MsgLength]

while BAUDCON1.6 = 0 ' Check RCIDL bit

wend

RXoccurred = 1 ' Set flag

Marker1 = 0

@ INT_RETURN

;--- Subroutines ---------------------------------------------------------------

Start:

@ INT_ENABLE RX_INT ; Enable USART Receive interrupts

while RXoccurred = 0 ' Wait for message

wend

Marker2 = 1

strcpy MsgData , Incoming , 80

pause 50

Marker2 = 0

Marker1 = 1

LCDOUT $FE, 1

LCDOUT $FE, $80, Value0, Value1, Value2, Value3, Value4, _

Value5, Value6, Value7, Value8, Value9, _

Value10, Value11, Value12, Value13, Value14, _

Value15, Value16, Value17, Value18, Value19

LCDOUT $FE, $C0, Value20, Value21, Value22, Value23, Value24, _

Value25, Value26, Value27, Value28, Value29, _

Value30, Value31, Value32, Value33, Value34, _

Value35, Value36, Value37, Value38, Value39

LCDOUT $FE, $94, Value40, Value41, Value42, Value43, Value44, _

Value45, Value46, Value47, Value48, Value49, _

Value50, Value51, Value52, Value53, Value54, _

Value55, Value56, Value57, Value58, Value59

LCDOUT $FE, $D4, Value60, Value61, Value62, Value63, Value64, _

Value65, Value66, Value67, Value68, Value69, _

Value70, Value71, Value72, Value73, Value74, _

Value75, Value76, Value77, Value78, Value79

Marker1 = 0

EndlessLoop:

goto EndlessLoop

end

Both RX programs used same base code, only changed array and added strcpy.

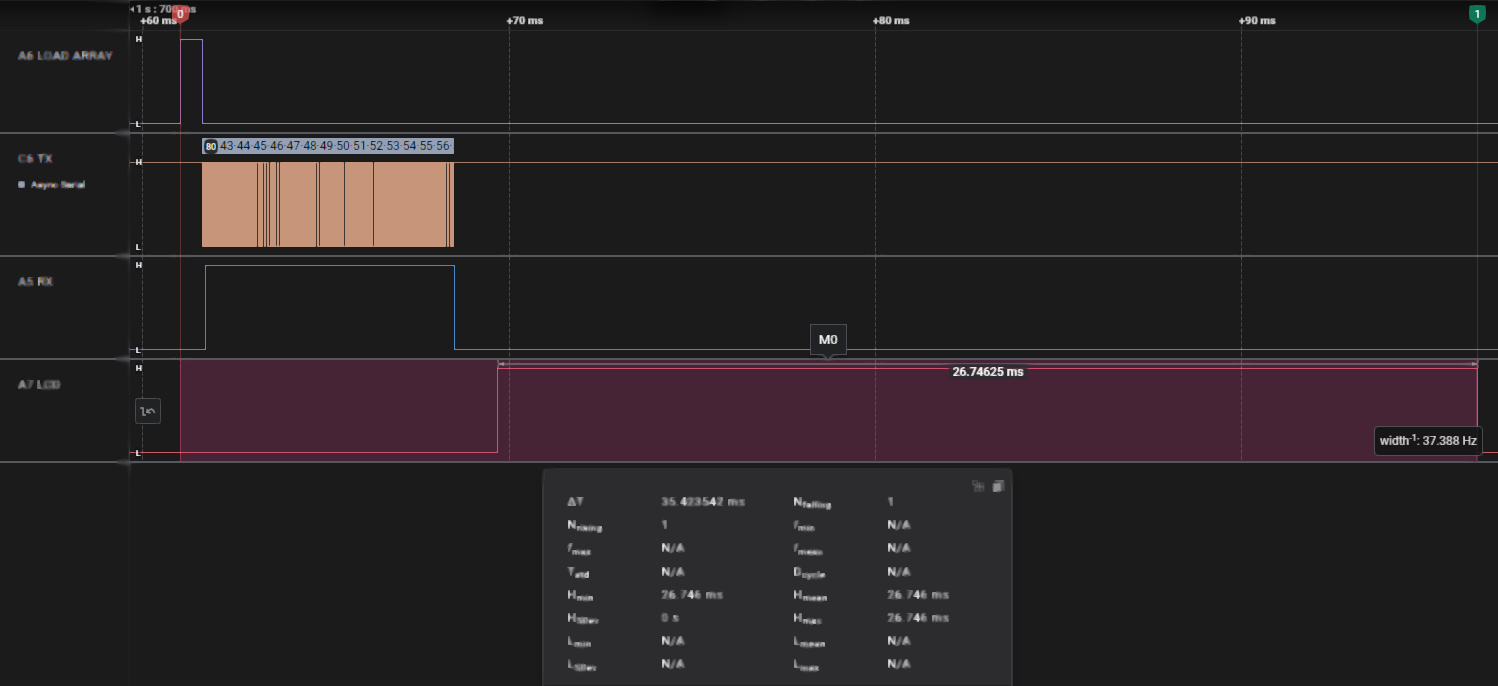

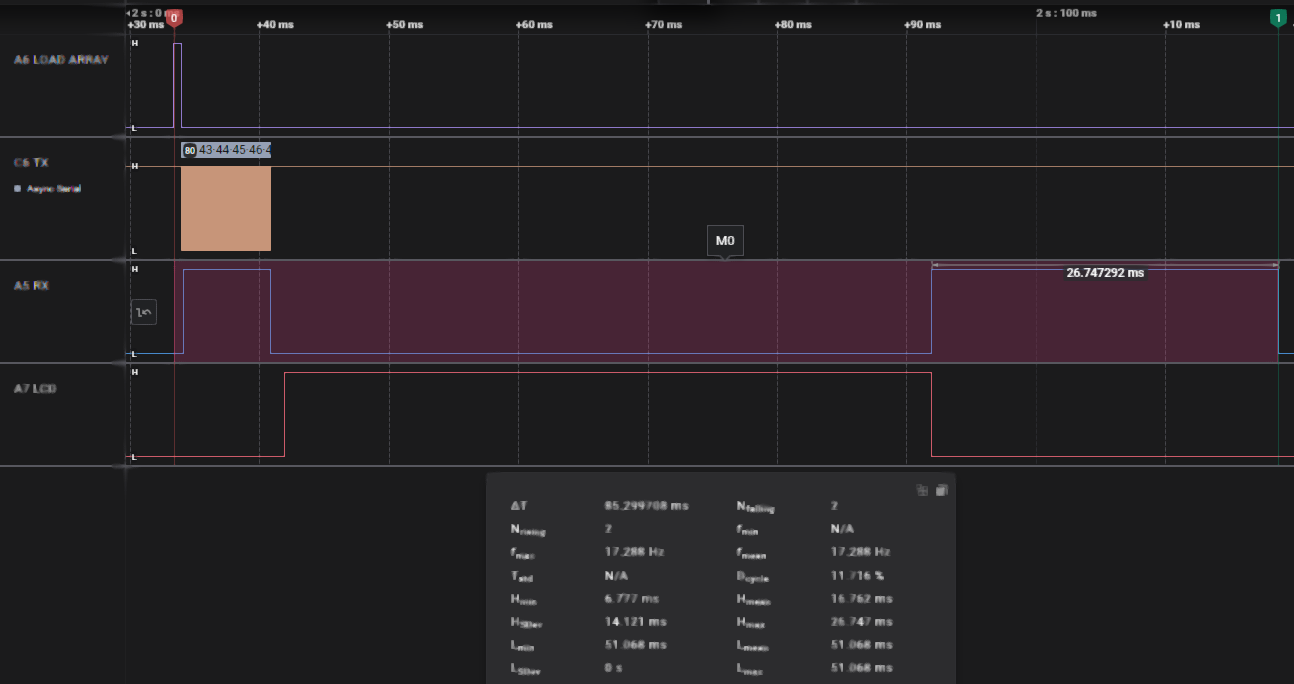

Saleae probe timings from before Load Array in TX to after Lcdout in RX

TX/RX using aliases, 35.4 mSec:

TX/RX using strcpy, now 85.2 mSec, adds 50.0 mSec step during strcpy:

LCD displayed properly "+" to "z":

Bookmarks