PIC18F14K50 USB Not Working

PIC18F14K50 USB Not Working

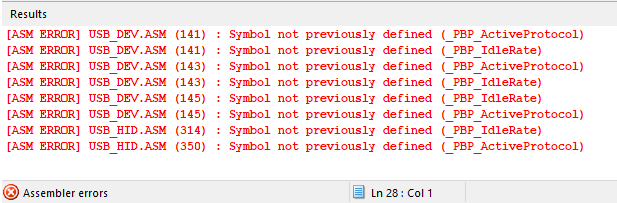

Okay, it looks like I'm stuck with the 18F4550 for my USB projects. Nothing else seems to work for me. I'm trying to just compile this program with the Include "descript.bas", but it doesn't work. This descript file works just fine with the 18F4550. I checked the USB_DEV.ASM and USB_HID.ASM files, but I don't know what the problem is. It might be an easy fix, but this assembler language is not my best friend. Any help is appreciated. Thanks, Robert

Code:

Include "descript.bas" ' Include the USB & HID descriptors

Define OSC 16

OSCCON = %11110111

#CONFIG

CONFIG CPUDIV = NOCLKDIV ; No CPU System Clock divide

CONFIG USBDIV = OFF ; USB clock comes directly from the OSC1/OSC2 oscillator block; no divide

CONFIG FOSC = IRC ; Internal RC oscillator ??????

CONFIG PLLEN = ON ; Oscillator multiplied by 4

CONFIG PCLKEN = ON ; Primary clock enabled

CONFIG FCMEN = OFF ; Fail-Safe Clock Monitor disabled

CONFIG IESO = OFF ; Oscillator Switchover mode disabled

CONFIG PWRTEN = OFF ; PWRT disabled

CONFIG BOREN = OFF ; Brown-out Reset disabled in hardware and software

CONFIG BORV = 19 ; VBOR set to 1.9 V nominal

CONFIG WDTEN = OFF ; WDT is controlled by SWDTEN bit of the WDTCON register

CONFIG WDTPS = 512 ; 1:512

CONFIG HFOFST = OFF ; The system clock is held off until the HFINTOSC is stable.

CONFIG MCLRE = OFF ; RA3 input pin enabled; MCLR disabled

CONFIG STVREN = OFF ; Stack full/underflow will not cause Reset

CONFIG LVP = OFF ; Single-Supply ICSP disabled

CONFIG BBSIZ = OFF ; 512W boot block size

CONFIG XINST = OFF ; Instruction set extension and Indexed Addressing mode disabled (Legacy mode)

CONFIG DEBUG = OFF ; Background debugger disabled, RA0 and RA1 configured as general purpose I/O pins

CONFIG CP0 = ON ; Block 0 code-protected

CONFIG CP1 = ON ; Block 1 code-protected

CONFIG CPB = OFF ; Boot block not code-protected

CONFIG CPD = OFF ; Data EEPROM not code-protected

CONFIG WRT0 = OFF ; Block 0 not write-protected

CONFIG WRT1 = OFF ; Block 1 not write-protected

CONFIG WRTC = OFF ; Configuration registers not write-protected

CONFIG WRTB = OFF ; Boot block not write-protected

CONFIG WRTD = OFF ; Data EEPROM not write-protected

CONFIG EBTR0 = OFF ; Block 0 not protected from table reads executed in other blocks

CONFIG EBTR1 = OFF ; Block 1 not protected from table reads executed in other blocks

CONFIG EBTRB = OFF ; Boot block not protected from table reads executed in other blocks

#ENDCONFIG

"No one is completely worthless. They can always serve as a bad example."

Anonymous

Bookmarks