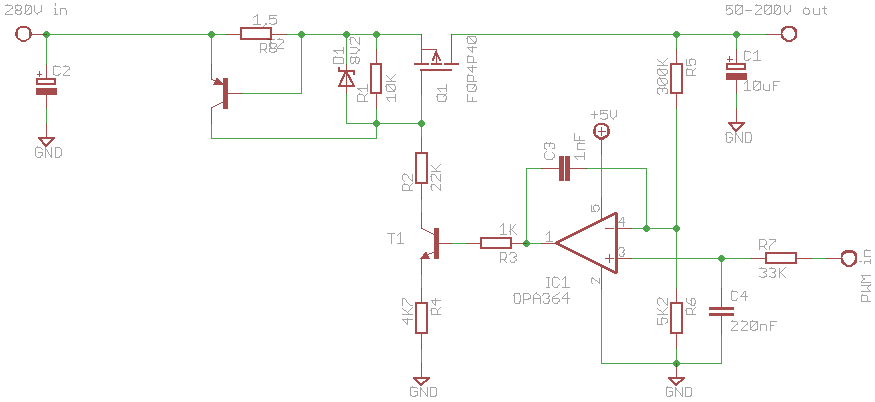

I am designing a HV Power Supply controlled by a PWM signal (from a PIC).

The problem is that either of the attached circuits for the current limit does not work. Even with no current load, the MOSFET is not allowed to work, as if the transistors are shorting the G-S of the MOSFET.

Can anyone explain why is that happening? I though of leakage current but whatever transistor I tried the same happens.

Ioannis

Bookmarks