Hi Jim,

I just tried it here, 18F25K20 running at 64MHz.

Code:

TRISC = %10000000 '

TRISB = %00000000 '

Datapin var PortB.7 ;

Clockpin var PortB.6 ;

CS var PortB.5

PortB = %00100000 ' Setup initial pin states.

Pause 100

Start:

CS = 0

shiftout Datapin, Clockpin, 1, [%10001000]

CS = 1

Pause 100

Goto Start

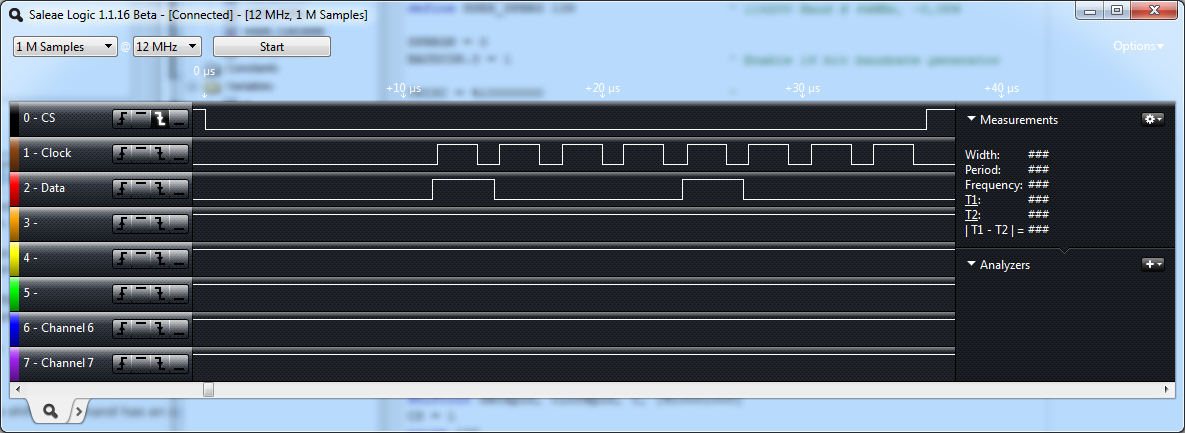

As you can see I'm using MODE 1 (clock idles low, MSB first). I captured the result with my logic analyzer:

As you can see the datapin is indeed true before the rising edge of the clock, throwing some markers on it tells me that the datapin goes true 250nS before the rising edge of the clock signal but that will be different depending on the oscillator speed.

Do you have anything else on your data output pin (like a LED or, worse, something capacitive) that can possible load output driver making its risetime increase?

/Henrik.

Bookmarks