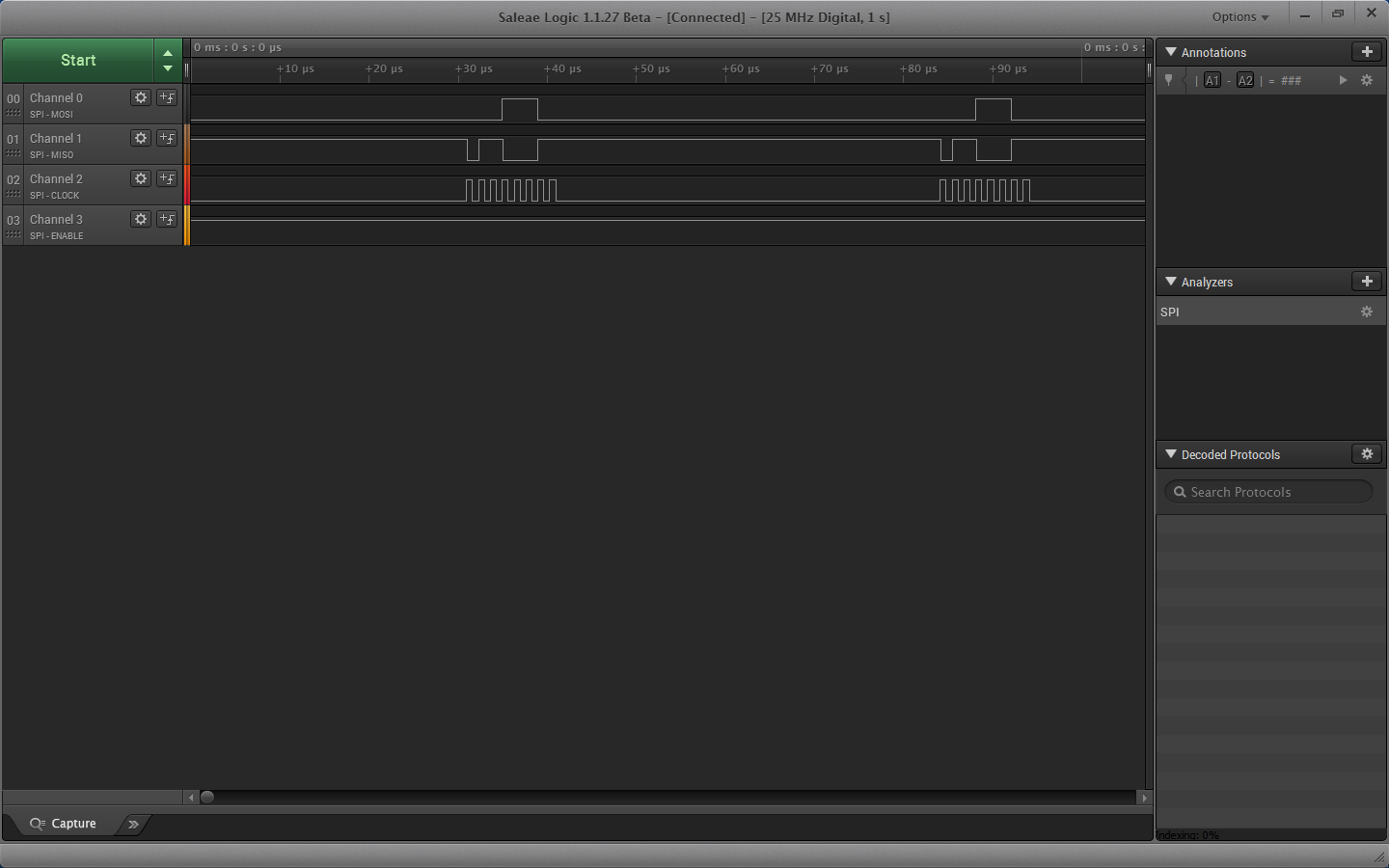

I've got successful SPI communication between an 18F2550(master) and a 16F887(slave) with the slave SS pin enabled. Here is the code for my master and slave and an analyzer screenshot of successful communication with the master sending 28 and the slave returning 99, as expected:

Code:'SPI MASTER CODE for 18F2550 DEFINE OSC 20 pause 5000 cs VAR PORTB.7 cs2 VAR PORTB.6 SSPEN VAR SSPCON1.5 CKP VAR SSPCON1.4 SMP VAR SSPSTAT.7 CKE VAR SSPSTAT.6 BF VAR SSPSTAT.0 sig VAR byte sig2 VAR byte TRISA = %11111111 ' Set PORTA to all input TRISB = %00000001 TRISC.7 = 0 cs = 1 cs2 = 1 SSPEN = 1 SSPCON1.0 = 0 SSPCON1.1 = 1 SSPCON1.2 = 0 SSPCON1.3 = 0 CKP = 0 CKE = 0 SMP = 0 mainloop: cs = 0 SSPBUF = 28 while BF = 0 : wend sig = SSPBUF cs = 1 pauseus 100 goto mainloop ENDThe problem is that when I test this without dropping the SS line low to enable I still see the MISO transmission from my slave. I thought that if SS does not go low then the slave chip would not be enabled? Why would the slave respond even when its SS pin is high as seen in the screenshot below from my analyzer?Code:'SPI SLAVE CODE for 16F887 DEFINE OSC 20 SSPEN VAR SSPCON.5 CKP VAR SSPCON.4 SMP VAR SSPSTAT.7 CKE VAR SSPSTAT.6 BF VAR SSPSTAT.0 TRISA = %11111111 TRISB = %11111111 TRISC = %11011111 TRISD = %00000000 SSPCON = %00000100 CKP = 0 CKE = 0 SMP = 0 SSPEN = 1 mainloop: while BF=0: wend SSPBUF = 99 goto mainloop END

It seems that my slave chip does not know it is in "SPI Slave mode, clock = SCK pin, SS pin control enabled". I'd like to work this out because when I add more slaves with their own SS lines from my master they all respond at the same time on the MISO line and the data is incorrect because they aren't individually enabling/disabling as expected.

Any insight would be greatly appreciated.

Bookmarks